Vol. No.8 Issue 01, January-June 2016 www.arresearchpublication.com

# DESIGN AND ANALYSIS OF VEDIC MULTIPLIER USING MICROWIND

Amita<sup>1</sup>, Nisha Yadav<sup>2</sup>, Pardeep<sup>3</sup>

<sup>1,2,3</sup>Student, YMCA University of Science and Technology/Electronics Engineering, Faridabad, (India)

#### ABSTRACT

Multiplication is the fundamental operation in Arithmetic and logical unit. In this paper we have designed a multiplier unit which is important part of ALU. In basic multiplication required addition, subtraction and shift operation. Simple linear multipliers had been designed already. But for fast multiplication, there is technique used Vedic mathematics in which delay and area increases very slowly as the number of bits increases. In this paper multiplier circuits have designed in DSCH tool and simulated in Microwind using CMOS 180nm technology. Simple Braun Array and Vedic multipliers are compared in terms of power, delay and area. By the analysis of multiplier circuits using Microwind tool found that the delay of proposed Vedic multiplier is reduced by 69.8%.Hence it gives better performance that Braun Array multiplier.

Keywords: Area, Braun Array multiplier, CMOS technique, Delay, Full adders, Power dissipation.

### I. INTRODUCTION

In VLSI designs today, the device dimensions are shrinking exponentially and the circuit complexity is also growing. Further, device scaling is limited by the power dissipation, demanding for better power optimization technique. As the scale of integration keep growing, more and more signal processing systems are being implemented on VLSI chips. These signal processing applications not only demand great computation capacity but also consume considerable amounts of energy. While performance, area becomes major design goals, power consumption has become important parameter in today's VLSI system design.

An ALU is a fundamental building block of a central processing unit in any computing system. The ALU perform the arithmetic operations such as addition, multiplication etc. So the need of fast multiplication is important in DSP systems. In basic multiplication required addition, subtraction and shift operation. But for fast multiplication, there is technique used Vedic mathematics technique in the number of bits increases. Low power multipliers (parallel and serial) have wide applications in signal processing. Therefore Braun array multiplier and Vedic multipliers has been designed and provide good area optimization and less power dissipation. CMOS technique is used for full adders and multipliers design. All the circuits are designed in DSCH and simulated in Microwind tool. Braun array and Proposed Vedic multipliers are compared in terms of power, delay and area.

#### **II. ANALYSIS OF ADDERS**

Adders are commonly found in the critical path of many building blocks of microprocessors and digital signal processing chips. Adders are essential not only for addition, but also for subtraction, multiplication, and division. Addition is one of the fundamental arithmetic operations. There is a necessity of Fast adders in

## International Journal of Electrical and Electronics Engineers Vol. No.8 Issue 01, January-June 2016 www.arresearchpublication.com

ALUs, for computing memory addresses, and in floating point calculations. A fast and accurate operation of a digital system is greatly influenced by the performance of the resident adders. The most important for measuring the quality of adder designs in the past were propagation delay, and area.

#### Figure 1.1 Full adder

#### **III. ANALYSIS OF MULTIPLIERS**

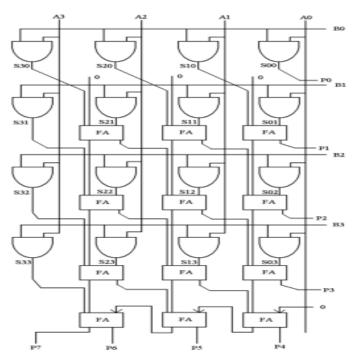

**Braun Array Multiplier:-** The simplest parallel multiplier is the Braun array. All the partial products are computed in parallel, and then collected through a cascade of Carry Save Adders. The completion time is limited by the depth of the carry save array, and by the carry propagation in the adder. Note that this multiplier is only suited for positive operands. Braun array multiplier consist of AND gates and full adders. Each of  $a_i x b_i$  product bits is arranged in parallel with AND gates. Each partial product can be added to previous sum of partial product.

#### Vedic mathematics multiplication technique

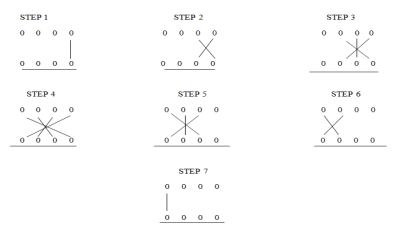

The proposed Vedic multiplier is based on the Vedic multiplication formulae (Sutras). These Sutras have been traditionally used for the multiplication of two numbers in the decimal number system. In this work, we apply the same ideas to the binary number system to make the proposed algorithm compatible with the digital hardware. Vedic multiplication based on following algorithm, which is discussed below:

#### Technique used

#### Urdhva Tiryakbhyam Sutra

The multiplier is based on an algorithm Urdhva Tiryakbhyam (Vertical & Crosswise) of ancient Indian Vedic Mathematics. Urdhva Tiryakbhyam Sutra is a general multiplication formula applicable to all cases of multiplication. It literally means "Vertically and crosswise". It is based on a novel concept through which the generation of all partial products can be done with the concurrent addition of these partial products.

Vol. No.8 Issue 01, January-June 2016 www.arresearchpublication.com

Figure 1.2 Braun array multiplier

## 1) Multiplication of two decimal numbers- Line diagram

### **IV. PERFORMANCE PARAMETERS**

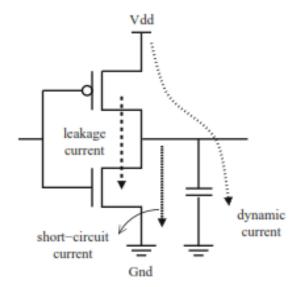

#### 1) Power Dissipation

Power dissipation is a measure of the power consumed by the logic gate when fully driven by all its input. The D.C or average power dissipation is the product of D.C supply voltage and the mean current taken from the supply.

Vol. No.8 Issue 01, January-June 2016 www.arresearchpublication.com

#### **Figure 1.4 Power dissipation in cmos**

### 2) Delay

The delay can be defined as time required to reach 0.5 Vdd of output from the 0.5V of input.

Delay of multiplier=  $(n-1)*m*T_{\text{full adder}}$  n=number of multiplicand

#### 3) Area

The area needed for Vedic square multiplier is very small as compared to other multiplier architectures i.e. the number of devices used in Vedic square multiplier are 259 while Booth and Array Multiplier is 592 and 495 respectively. Thus the result shows that the Vedic square multiplier is smallest and the fastest of the reviewed architectures

#### **V. SIMULATION RESULTS**

#### Braun array multiplier:

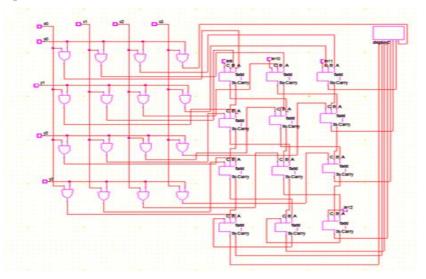

Figure 1.5 Schematic of Braun Array multiplier

Vol. No.8 Issue 01, January-June 2016

www.arresearch publication.com

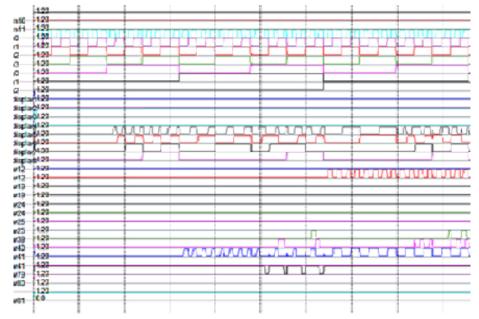

## WAVEFORM:-

Figure 1.6 output waveform of Braun array

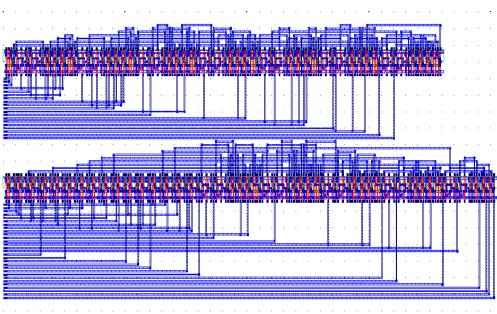

Figure 1.7 Layout of Braun array multiplier

Vol. No.8 Issue 01, January-June 2016 www.arresearchpublication.com

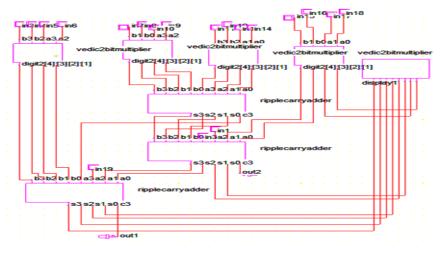

## **Proposed Vedic Multiplier**

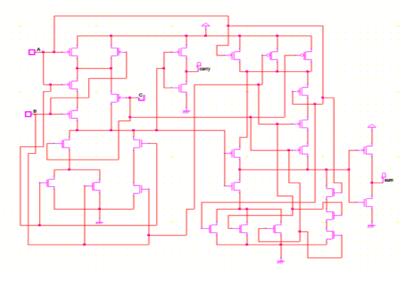

Figure 1.8 Schematic of 4 bit Vedic multiplier

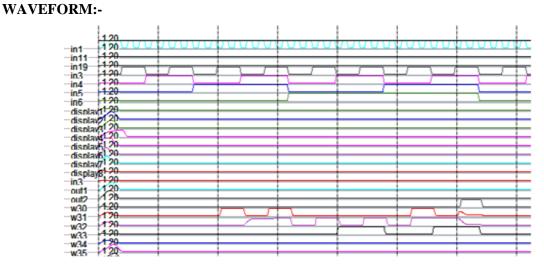

Figure 1.8 Output waveform of Vedic multiplier

## Figure 1.9 Layout of Vedic multiplier

## LAYOUT:-

Vol. No.8 Issue 01, January-June 2016

www.arresearchpublication.com

## VI. COMPARISON AND DISCUSSION

There are different types of multipliers are designed using 180nm.

#### 4\*4 multipliers 180nm technology (BSIM4 model)

| Multipliers     | Width | Height | No. Of | No. of | S.Area                     | Power     | Delay(ps) |

|-----------------|-------|--------|--------|--------|----------------------------|-----------|-----------|

|                 | (um)  | (um)   | PMOS   | NMOS   | ( <b>um</b> <sup>2</sup> ) | Diss.(mw) |           |

| Braun array     | 122   | 31     | 228    | 228    | 4522                       | 0.509     | 38        |

| Vedic<br>multi. | 124   | 32     | 248    | 248    | 5047                       | 0.156     | 96        |

Table 1.1

Simulation results of Braun array multiplier and Vedic multiplier compared in the terms of power, delay and area. Width and height of layouts are changes according to technology.

### **VII. CONCLUSION**

The proposed Vedic multiplier is designed using CMOS technique and it performed with 69.35 less power dissipation as compared to Braun array multiplier. The no of transistor count increases but gives less delay and high speed as compare to other multipliers. Vedic Multipliers are used in fields of Digital Signal Processing (DSP), Chip Designing, Discrete Fourier Transform (DFT), and High Speed Low Power VLSI circuits. In future power reduction is main aim for digital design.

### REFERENCES

- S. Kiruthika, R.Nirmal Kumar, Dr. S. Valarmathy "Comparative Analysis of 4-Bit Multipliers Using Low Power 8-Transistor Full Adder Cells" International Journal of Emerging Technology and Advanced Engineering, (ISSN 2250-2459, ISO 9001:2008 Certified Journal, Volume 3, Issue 1, January 2013)

- [2] Varsharani V.Haibatpure,Parbha S. Kalsiwal, B.P. Patil "Performance Evaluation of Proposed Vedic Multiplier In Microwind" International Journal of Communication Engineering Applications-ISSN: 2230-8520; e-ISSN: 2230-8539 june 2012.

- [3] C. Senthilpari, Ajay Kumar Singh, K. Diwakar "Design of a low-power, high performance, 8\*8 bit multiplier using a Shannon-based adder cell" IEE Electr. (2008).

- [4] Nirlakalla Ravi, Anchula Satish, Dr. Talari Jayachandra Prasad and Dr. Thota Subba Rao, "A New Design for Array Multiplier with Trade off in Power and Area", IJCSI International Journal of Computer Science Issues, Vol. 8, Issue 3, No. 2, May 2011

- [5] Yano, K., Yamanaka, T., Nishida, T., Saito, M., Shimohigashi, K., and Shimizu, A., "A 3.8-ns CMOS 16b multiplier using complementary pass-transistor logic" IEEE Journal of Solid-State Circuits, vol. 25, 1990, pp. 388-395.

- [6] R. Zimmerman and W. Fichtner, "Low-power logic styles: CMOS versus pass-transistor logic", IEEE J. Solid-State Circuits, vol. 32, no.7, Jul. 1997, pp. 1079–1090.

## International Journal of Electrical and Electronics Engineers Vol. No.8 Issue 01, January-June 2016 www.arresearchpublication.com

- [7] Suzuki .M, ohkubo.N, yamanka .T, Shimizu.A and Sasakim.K, "A 1.5 ns 32-b Cmos ALU in double pass transistor logic", IEEE Journal of Solid State Circuits, vol28,1993,pp.1145-1151

- [8] Ilham Hassoune, Denis Flandre, Ian O Connor, and Jean-Didier Legat,—ULPFA: A "New Efficient Design of a Power-Aware Full Adder", IEEE Transactions On Circuits And Systems- I: Regular Papers, vol. 57, no. 8, August 2010.

- [9] S.S.Kerur, Prakash Narchi, Jayashree C N, Harish M Kittur and Girish V Implementation of Vedic Multiplier For Digital Signal Processing International conference on VLSI communication & instrumentation (ICVCI), 2011.