International Journal of Electrical and Electronics Engineers Vol. No.8 Issue 01, January-June 2016 www.arresearchpublication.com

# **Performance Evolution of DDR3 SDRAM**

# **Controller for Communication Networks**

# U.Venkata Rao<sup>1</sup>, G.Siva Suresh Kumar<sup>2</sup>, G.Phani Kumar<sup>3</sup>

<sup>1,2,3</sup>Department of ECE, Sai Ganapathi Engineering College, Visakhaapatnam, (India)

# ABSTRACT

The memory technologies are advantageous for high speed operation and performance as the system bandwidth continues to increase. The memories with high density, high bandwidth and low device cost are DDR3 SDRAM which is the third generation of DDR memories. However, because of high speed interface technology and complex instruction based memory a special purpose memory interface is necessary for optimizing the burst access to increase data throughput. In this paper, a specific purpose DDR3 interface for high performance look up table is proposed with Hash CAM scheme.

### Keywords: DDR3, SDRAM, Verilog.

# I. INTRODUCTION

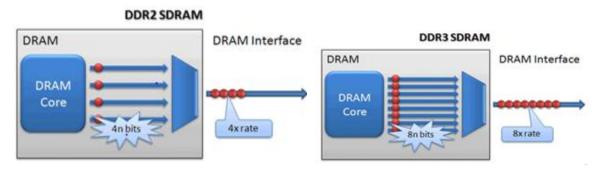

One of the most important aspects of a computer is its ability to store large amount of information called memory specifically, its random access memory (RAM). With improvements in processor speeds, RAM memory has evolved into high performance RAM chipsets called DDR SDRAMs.It doubles the processing rate by making a data fetch on both rising & falling edge of a clock cycle. This is in contrast to the older SDR SDRAM.DDR3 SDRAM transfers the data at twice the rate of DDR2 SDRAM which enables higher bandwidth while DDR2 uses 4n-prefetch and DDR3 uses 8n-prefetch [1]. A 64-bit DDR3 SDRAM may achieve a ransfer rate up to 64 times the memory clock speed in megabytes per second(MB/s).In addition, the DDR3 standard permits the chip capacities of up to 8 gigabits Content Addressable Memory (CAM) based techniques are widely used in network equipment for fast table look up[2]. When it comes to RAM technology and CAM technology, CAM technology is confined in few aspects like hardware cost, memory density and power dissipation. Recently a HASH-CAM circuit [3], which combines the merits of hash algorithm and the CAM function, was proposed to replace pure CAM based look up circuits with comparable performance, higher memory density and lower cost. Efficient DDR bandwidth [4] utilization is the major challenge for lookup functions that exhibit short and random memory access patterns. Compared with DDR SDRAM the voltage of DDR3 SDRAM was lowered from 2.5V to 1.5V. This improves power consumption and heat generation, as well as enabling more dense memory configurations for higher capacities. The off-chip low cost, high density DDR memory technology has now become an attractive alternative for proposed HASH-CAM based lookup circuit. However DDR technology optimized for burst access. This paper presents DDR3 SDRAM interface architecture to achieve high speed operation by using Xilinx FPGA technology.

# International Journal of Electrical and Electronics Engineers 🛕 🗖

Vol. No.8 Issue 01, January-June 2016

## www.arresearchpublication.com

### **II. BRIEF REVIEW OF DDR/SDRAM**

DDR memory's primary advantage is the ability to fetch the data on both rising falling edge of a clock Cycle, doubling the data rate for a clock cycle. Memory temporization is given through a series of numbers, such as 2-3-2-6-T1,3-4-4-8 or 2-2-2-5 for DDR1. These numbers indicate the number of clock pulses that it takes the memory to perform a certain operation-the smaller the number faster the operation. The operations that these numbers represent the CL-tRCD-tRP-tRS-CMD[5].

**CL**: Column address Strobe (CAS) latency is the time it takes between the processor asking memory for data and memory returning it.

**tRCD**: ROW Address Strobe (RAS) to CAS delay is the time it takes between the activation of the row (RAS) and the column (CAS) where data is stored in the matrix.

**tRP**: RAS precharge is the time between disabling the access to a row of data and the beginning of the access to another row of data.

**tRAS**: Active to precharge delay is how long the memory has to wait until the next access to memory can be initiated.

**CMD**: Command rate is the time between the memory chip activation and when the initial starting command may be sent to the memory. But this value may not be informed. Because of the burst write/read mode and the multi bank architecture, simultaneous operations on different banks are allowed in SDRAMs. We can achieve high memory bandwidth by scheduling the memory access to each and every bank.

Many SDRAMs focus on bank control and data access sequences to achieve a better system performance. To improve memory bandwidth [6] and power consumption in video applications, new memory-interface architecture is proposed. An address-translation technique can be adopted as architecture in order to utilize the fact that video processing algorithms have memory-access patterns which are regular. We can minimize the number of overhead cycles by translation which are needed for row-activations in synchronous DRAM (SDRAM).

The architecture of the present video processing[7] units in consumer systems is usually based on various forms of processor .The present video processing unit architecture in consumer system is usually based on various types of processor hardware making communication with an off-chip SDRAM memory. The general examples are MPEG encoders and decoders and high end television systems. Based on the dual-core platform, the memory management system for multimedia application is performed. In order to reduce the memory bus transition and

# International Journal of Electrical and Electronics Engineers Vol. No.8 Issue 01, January-June 2016 www.arresearchpublication.com

have efficient bus bandwidth, 2 steps store optimization in control level has been adopted and nearly 35% bus efficiency increase is observed when compared with before scheme. To compliment different master requirements, a reasonable schedule level arranges memory access priority.

## **III.DESIGN METHODOLOGY**

DDR3 SDRAM devices are the next generation devices in the DDR SDRAM family. These devices use 1.5V signaling.DDR3 SDRAM devices use DDR architecture to achieve high speed operation .The memory operates using a differential clock provided by the controller.DDR3 memory is more flexible to be accessed with fewer bank conflicts. The proposed Hash-CAM based lookup circuit is shown in fig 2.

# Fig2:Hash-CAM lookup circuit using DDR3 SDRAMs

The original data and reference address information are stored in DDR3 SDRAM.A data is given to the Hash-CAM circuit where an address is generated. The translation of instructions and addresses is done when the address value is sent from DDR3 SDRAM interface which is later recognized by DD3 memory. The stored data &addresses in the memory are read back to the Hash-CAM circuit in order to validate the match.

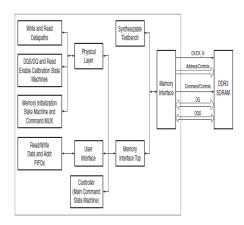

A sample user backend and synthesizable test bench block is provided as part of the DDR3 reference design. The backend provides address and data patterns to test read and write accesses between the memory device and the memory interface (DDR3 controller and Physical layer). The backend includes the following blocks: backend state machine, read data comparator, and a data generator module. The data generation module generates the various address and data patterns that are written to the memory.

### Fig3:DDR3 SDRAM interface

A bidirectional data strobe (DQS) [8] is transmitted along with the data for use in data capture at the receiver.DQS is strobe transmitted by the DDR3 SDRAM device during Read and by the controller while writing DQS when it is center aligned with data for Writes and edge aligned data for Reads.

# International Journal of Electrical and Electronics Engineers

Vol. No.8 Issue 01, January-June 2016

www.arresearchpublication.com

# IV. DDR3 SDRAM COMMANDS

Commands are registered at every positive edge of the clock. Read and Write accesses to the DDR3 SDRAM device are burst oriented .Accesses begin with the registration of an active command, which is then followed by Read or Write command.

### Precharge Command

The precharge command is used to deactivate the open row in a particular bank. The bank is available for subsequent row activation for a specified time after the precharge command is issued.

### **Auto Refresh Command**

For every 7.8  $\mu$ s the DDR3 device must be refreshed. Within the controller, the circuit to flag the Auto Refresh Command is built. With the help of system clock, the controller which is divided by 16, to make the counter refresh.

### **Active Command**

Within a back, the DDR3 SDRAM memory issues Read or Write commands, and then by using a Active Command a row in the bank is activated, Later a row is opened, read or write commands to the row are issued.

### **Read Command**

The Read command is used to initiate a burst read access to an active row. After the read burst is over, the row is still available for subsequent access until it is precharge.

### V. EXPERIMENTAL RESULTS AND ANALYSIS

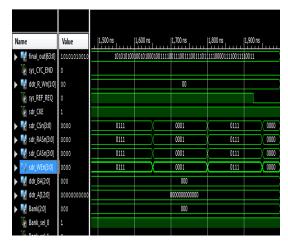

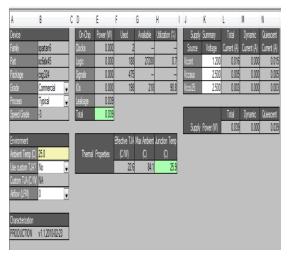

In this paper a high speed DDR3 SDRAM Interface has been designed with 64-bit data transfer which synchronizes the transfer of data between DDR RAM and external peripheral devices like host computer and laptop and so on. The simulation results for top module are shown in figure4. The complete lookup circuit was simulated using Xilinx technology .The off-chip power dissipation in this work is 39mW is shown in fig5. Reduced power consumption due to 90nm fabrication technology. Prefetch buffer is doubled to 8 bits to further increase performance.

Fig4: DDR3 SDRAM Top Module simulation results

# **Timing Summary:**

Speed Grade: -3

# International Journal of Electrical and Electronics Engineers Vol. No.8 Issue 01, January-June 2016

# rs AR JEEE ISSN 2321 - 2055

www.arresearchpublication.com

Minimum period: 4.616ns

(Maximum Frequency: 216.638MHz)

Minimum input arrival time before clock:5.812ns

Maximum output required time after clock: 3.856ns

# Fig5: Power Analysis of DDR3 SDRAM

Table 1.Performance of DDR3 Hash-CAM lookup Circuit

| Hash-CAM data width     | 64 bits |

|-------------------------|---------|

| Hash-CAM table entrants | 256K    |

| CAM-RAM depth           | 512     |

| Hash Function           | CRC-16  |

| Lookup Frequency        | 216MHz  |

| Combinational/Memory    | 292     |

| ALUTs                   |         |

| Registers               | 20747   |

The above experimental results clearly validate the expected performance of the proposed DDR3 SDRAM interface architecture. For a given random look up the DDR3 peak memory bandwidth can be achieved.

# VI. CONCLUSION

An advanced DDR3 SDRAM interface architecture for communication networks is proposed. 64bit data can be transferred between DDR RAM and external peripherals. For increasing the performance of DDR3 SDRAM, Hash Cam technology is used. The Performance of DDR3 SDRAM are evaluated with SDR SDRAM, DDR1 SDRAM, and DDR2 SDRAM

interface for Communication Networks. The data transfer of DDR3 SDRAM is twice that of DDR2 SDRAM. The off chip power dissipation is 39mW. The design was successfully synthesized using verilog HDL and simulated using Model Sim.

# International Journal of Electrical and Electronics Engineers Vol. No.8 Issue 01, January-June 2016 www.arresearchpublication.com

## REFERENCES

- 1 .Md.Jahid Hasan, Rukhsana Sumaiya Misha,"Intlligent High Performance Memory Access Technique in Aspect of DDR3 ", *Volume 3, Issue 2 (Sep. Oct. 2013), PP 17-22.*

- A.J.McAuley, et al, "Fast Routing Table Lookup Using CAMs", Proceedings on 12<sup>th</sup> Annual Joint Conference of the IEEE Computer and Communications Societies (INFOCOM), Vol.3, March 1993,pp.1382 – 1391.

- X.Yang, et al, "High Performance IP Lookup Circuit Using DDR SDRAM", IEEE International SOC Conference (SOCC), Sept. 2008, pp. 371-374.

- G.Allan, "The Love /Hate Relationship with DDR SDRAM Controllers ", MOSAID Technologies Whitepaper, 2006.

- DDR3 SDRAM Specification (JESD79-3A), JEDEC Standard, JEDEC Solid State Technology Association, Sept 2007.

- .Kim, et al, "High-Performance and Low-Power Memory Interface Architecture for Video Processing Application", IEEE Transactions on Circuit and Systems for Video Technology, Vol.11, NOV.2001, pp.1160-1170.

- 7. E.G.T.Jaspers, et al,"Bandwidth Reduction for Video Processing in Consumer Systems",IEEE Transactions on Consumer Electronics,vol.47,No.4,Nov.2001.

- 8. Shabana Aqueel, Kavita Khare, "A High Performance DDR3 SDRAM Controller", (IJEEE), Volume1, Issue1, 2011.